- 您现在的位置:买卖IC网 > Sheet目录1993 > DS1372U+T&R (Maxim Integrated Products)IC BINARY COUNTER 32-BIT 8-USOP

conditions. The DS1372 operates as a slave on the I2C

bus. Connections to the bus are made through the SCL

input and open-drain SDA I/O lines. Within the bus

specifications, a standard mode (100kHz maximum

clock rate) and a fast mode (400kHz maximum clock

rate) are defined. The DS1372 works in both modes.

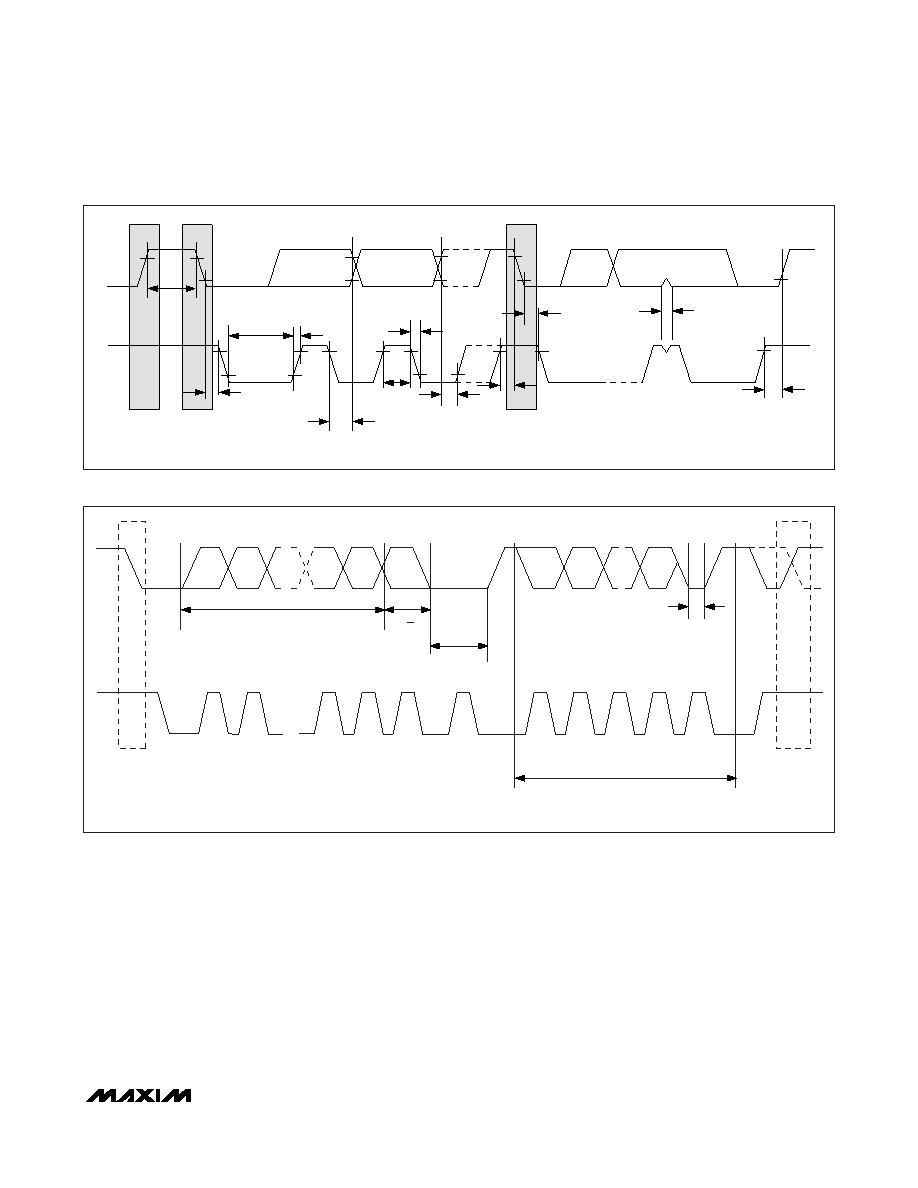

The following bus protocol has been defined (Figure 5):

Data transfer can be initiated only when the bus is

not busy.

During data transfer, the data line must remain stable

whenever the clock line is high. Changes in the data

line while the clock line is high are interpreted as

control signals.

DS1372

_______________________________________________________________________________________

9

SDA

SCL

tHD:STA

tLOW

tHIGH

tR

tF

tBUF

tHD:DAT

tSU:DAT

REPEATED

START

tSU:STA

tHD:STA

tSU:STO

tSP

STOP

START

Figure 4. Data Transfer on I2C Serial Bus

STOP

CONDITION

OR REPEATED

START

CONDITION

REPEATED IF MORE BYTES

ARE TRANSFERED

ACK

START

CONDITION

ACK

ACKNOWLEDGEMENT

SIGNAL FROM RECEIVER

ACKNOWLEDGEMENT

SIGNAL FROM RECEIVER

SLAVE ADDRESS

MSB

SCL

SDA

R/W

DIRECTION

BIT

12

6

7

8

9

1

2

8

9

3–7

Figure 5. I2C Data Transfer Overview

I2C, 32-Bit, Binary Counter Clock with 64-Bit ID

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DS1374C-3#

IC RTC I2C W/CHARGER 16-SOIC

DS1375T+

IC RTC SERIAL W/ALARM 6-TDFN

DS1384FP-12+

IC CTRLR RTC WDOG 120NS 44-MQFP

DS1386P-8-120+

IC TIMEKEEPER RAM 64K 34-PCM

DS1388Z-3+T&R

IC RTC I2C W/CHARGER 8-SOIC

DS1391U-3+

IC RTC W/CHARGER 10-USOP

DS1394U-33+T&R

IC RTC SPI 3WIRE W/CHRGR 10-MSOP

DS14285SN+T&R

IC RTC W/NV RAM CNTRL 24-SOIC

相关代理商/技术参数

DS1374

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:I2C, 32-Bit Binary Counter Watchdog RTC with Trickle Charger and Reset Input/Output

DS1374_10

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:I2C, 32-Bit Binary Counter Watchdog RTC with Trickle Charger and Reset Input/Output

DS1374C-18

功能描述:实时时钟 I2C 32-Bit Binary Counter Watchdog RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1374C-18-

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:I2C, 32-Bit Binary Counter Watchdog RTC with Trickle Charger and Reset Input/Output

DS1374C-18#

功能描述:实时时钟 I2C 32-Bit Binary Counter Watchdog RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1374C-3

功能描述:实时时钟 I2C 32-Bit Binary Counter Watchdog RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1374C-3-

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:I2C, 32-Bit Binary Counter Watchdog RTC with Trickle Charger and Reset Input/Output

DS1374C-3#

功能描述:实时时钟 I2C 32-Bit Binary Counter Watchdog RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube